![]() Grâce à l’utilisation de la nouvelle technologie Smart Proof basée sur l’apprentissage automatique, ce logiciel de vérification formelle de troisième génération permet de prouver les propriétés 2 fois plus rapidement et accélère d’un facteur 5 l’exécution des tests de non-régression.

Grâce à l’utilisation de la nouvelle technologie Smart Proof basée sur l’apprentissage automatique, ce logiciel de vérification formelle de troisième génération permet de prouver les propriétés 2 fois plus rapidement et accélère d’un facteur 5 l’exécution des tests de non-régression.

Cadence Design Systems, annonce ce jour la troisième génération de sa plateforme de vérification formelle Cadence® JasperGold®, qui intègre une technologie d’apprentissage automatique (Machine Learning) et perfectionne les fonctions centrales de vérification formelle. Les améliorations apportées à cette plateforme permettent de relever les défis de capacité et de complexité qui caractérisent les systèmes sur puce (SoC) avancés, tout en augmentant la vitesse de vérification.

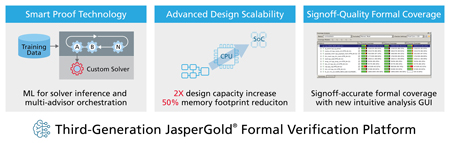

La nouvelle plateforme JasperGold marque la toute dernière étape des améliorations en cours sur l’orchestration et l’algorithme de solveur de preuve (proof solver). Cette plateforme intègre la technologie Smart Proof qui améliore la vitesse de vérification de toutes les applications JasperGold. La technique d’apprentissage automatique est utilisée pour sélectionner et paramétrer les solveurs en vue d’accélérer la délivrance de preuves dès la première tentative (first-time proofs). L’apprentissage automatique est également utilisé pour optimiser les opérations successives des tests de non-régression, que ce soit sur site ou sur le cloud. Grâce à la technologie Smart Proof, la vitesse de délivrance des preuves peut tre multipliée par 4 et jusqu’à 6 fois en non-régression.

« Avec la nouvelle plateforme intelligente JasperGold utilisée en mode standard (out of the box), nous avons mesuré en moyenne une accélération de 2X pour obtenir les preuves et de 5X pour l’exécution des tests de non-régression sur nos designs », a déclaré Mirella Negro Marcigaglia, responsable de la vérification des conceptions numériques, STMicroelectronics. « Nous constatons également une réduction de plus de 50 % des propriétés non convergentes. Ensemble, ces améliorations augmentent considérablement notre productivité dans le domaine de la vérification. »

À l’heure où les systèmes sur puce (SoC) sont toujours plus gros et plus complexes, le processus de compilation fixe la taille maximale du design et les ressources de calcul nécessaires pour lancer l’analyse formelle. Par rapport aux performances enregistrées l’année dernière, la nouvelle plateforme JasperGold se distingue par une capacité de compilation des designs multipliée par plus de 2, avec une réduction moyenne de 50 % de l’utilisation de la mémoire au cours de la phase de compilation. De plus, les ingénieurs peuvent moduler efficacement la capacité de conception grâce à des technologies de compilation parallèle avancées qui optimisent l’utilisation des ressources de calcul disponibles et en exécutant les preuves sur le cloud.

Les nouvelles technologies de couverture formelle de la plateforme permettent aux ingénieurs de valider complètement les blocs IP avec la plateforme JasperGold. Ces nouvelles technologies de validation (signoff) formelle bénéficient d’une précision « proof-core » accrue, de nouvelles techniques permettant de dériver une couverture pertinente à partir d’une chasse aux bogues approfondie (deep bug hunting) et de nouvelles vues d’analyse de couverture formelle. L’ensemble de ces fonctionnalités procure des métriques de couverture formelle de qualité « sign-off » et une clôture de vérification multimoteurs au niveau du circuit intégré complet.

« La première génération de la plateforme JasperGold a fait figure de pionnier sur le marché de la vérification formelle commerciale et de ses applications, tandis que la deuxième a intégré des technologies Cadence pour déployer un flot de vérification formelle chez tous les utilisateurs », a déclaré Ziyad Hanna, vice-président, Fabric and Formal Solutions, System & Verification Group chez Cadence. « Notre plateforme intelligente JasperGold de troisième génération marque une avancée considérable du cœur de la technologie formelle en s’appuyant sur l’apprentissage automatique pour apporter à nos clients de meilleures performances et des évolutivité tangibles. »

Partie intégrante de la Cadence Verification Suite, la plateforme de vérification formelle JasperGold offre une couverture exhaustive au sein de la plateforme de validation à base de métriques vManager™ Metric-Driven Signoff, qui associe les résultats formels fournis par JasperGold aux métriques de simulation Xcelium™ et d’émulation Palladium® afin d’accélérer la clôture de la totalité de la vérification. Cette plateforme s’inscrit dans le cadre de la stratégie System Design Enablement de Cadence qui permet aux fabricants de systèmes et de semiconducteurs de créer des produits finaux complets et différenciateurs avec une efficacité accrue. La suite « Cadence Verification Suite » se compose des meilleurs moteurs JasperGold, Xcelium®, Palladium® et Protium™, ainsi que des technologies et solutions de vérification qui augmentent la qualité et la productivité de conception, répondant ainsi aux exigences de vérification d’un large éventail d’applications et de secteurs industriels.