Elle est proposé par Cadence pour les secteurs de l’intelligence artificielle et de l’apprentissage automatique, de la 5G, du cloud computing et des réseaux.

Elle est proposé par Cadence pour les secteurs de l’intelligence artificielle et de l’apprentissage automatique, de la 5G, du cloud computing et des réseaux.

![]() Cette IP éprouvée sur le silicium est disponible dès aujourd’hui en grands volumes.

Cette IP éprouvée sur le silicium est disponible dès aujourd’hui en grands volumes.

![]() Elle supporte les systèmes sur puce multipuces sur substrats organiques.

Elle supporte les systèmes sur puce multipuces sur substrats organiques.

![]() Le débit nominal de 40 Gbits/s assure une bande passante unidirectionnelle pouvant atteindre 7 térabit/s par mm.

Le débit nominal de 40 Gbits/s assure une bande passante unidirectionnelle pouvant atteindre 7 térabit/s par mm.

![]() Le taux d’erreur binaire (BER) est meilleur que 10-15 sans correction d’erreur anticipée (FEC).

Le taux d’erreur binaire (BER) est meilleur que 10-15 sans correction d’erreur anticipée (FEC).

Cadence Design Systems, annonce ce jour sous la référence Cadence® UltraLink™D2D PHY IP, un nouveau bloc de propriété intellectuelle (IP) puce-á-puce sur couche physique (PHY) de haute performance et à faible temps de latence destiné aux applications de connectivité puce-à-puce (D2D-Die-to-Die) utilisées dans les secteurs de l’intelligence artificielle et de l’apprentissage automatique, des communications 5G, du cloud et des réseaux.

Cette nouvelle IP PHY puce-à-puce est une technologie critique destinée aux micro-puces et aux systèmes en boîtier, qui permet aux fabricants de systèmes sur puce de proposer des solutions davantage personnalisées qui allient des performances et des rendements plus élevés, tout en raccourcissant les cycles de développement et en abaissant les coûts grâce à une réutilisation plus efficace d’IP.

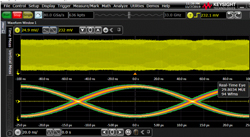

Le nouveau bloc IP puce-à-puce sur couche physique UltraLink fonctionne à un débit nominal pouvant atteindre 40 Gbits/s sur une interface série NRZ (Non-Return-to-Zero), assurant une bande passante unidirectionnelle de 1 Tbit/s par mm.. Les fonctions de correction d’alignement (built-in de-skew) et de brouillage/désembrouillage embarquées facilite l’intégration des systèmes. Alors que les solutions existantes requièrent au moins 30 % de fils en plus, le nombre limité de fils à savoir 28 pour une bande passante de 1 Tbit/s, simplifie le routage et abaisse potentiellement le coût du conditionnement mise en boitier. De plus, contrairement à certaines solutions puce-à-puce moins véloces qui nécessitent un interposeur silicium pour obtenir une bande passante identique, l’IP puce-à-puce sur couche PHY UltraLink apporte des avantages de coût significatifs grâce à la prise en charge de modules multi-puces (MMC) sur substrats organiques.

Enfin, cette IP présente un temps de latence aller-retour de seulement 5 ns entre le récepteur et l’émetteur, utilise en standard un codage NRZ (non-return-to-zero), et se caractérise par un taux d’erreurs binaire (BER) meilleur que 10-15 sans correction d’erreur anticipée (FEC : Forward Error Correction). Enfin, le bloc IP UltraLink est éprouvé sur silicium en technologie avancée 7 nm FinFET.