Synopsys lance IC Validator, réduisant significativement le temps de vérification physique des designs avancés TSMC inclus IC Validator dans son programme de qualification EDA pour la technologie 28 nm

Synopsys, Inc. (NASDAQ : SNPS), un leader du logiciel et de l’IP pour la conception et la fabrication de semi-conducteurs, annonce la solution de DRC/LVS IC Validator pour la vérification physique en cours de conception et la vérification finale (signoff) des designs avancés en 45 nanomètre (nm) et en deçà. Architecturé pour fournir la précision requise par les procédés technologiques les plus avancés, pour utiliser efficacement les calculateurs disponibles et pour une grande facilité d’usage, IC Validator franchit une étape dans la productivité lors de la vérification physique. IC Validator réduit le temps total de vérification physique grâce à : la vérification en cours de design, la réduction du nombre de ‘stream-out’, le traitement incrémental, la détection et la correction automatique des erreurs et l’accélération quasi linéaire sur les systèmes multi CPU. IC Validator disponible et prêt pour la production, il a été inclus par TSMC dans son programme de validation EDA pour la vérification finale des règles de dessin (DRC/LVS signoff), pour les technologies à partir du 28 nm.

« TSMC emploie des critères de qualification rigoureux pour assurer la précision du DRC/LVS lors de la vérification physique finale. Nous avons collaboré étroitement avec Synopsys durant le développement d’IC Validator et l’avons inclus dans notre programme de validation EDA 28nm, » dit S.T. Juang, senior directeur marketing pour l’infrastructure de conception chez TSMC. « Cette collaboration avec Synopsys a permis à IC Validator de montrer de bons résultats dans le récent des rapports de qualification des outils de vérification physique de TSMC. »

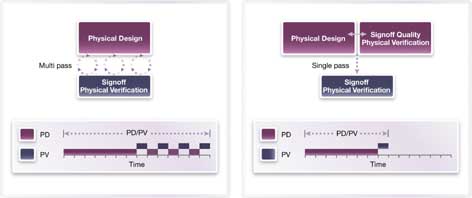

L’approche qui prévaut aujourd’hui pour la conception physique peut se décrire comme « dessiner puis vérifier » ; elle nessite de multiples itérations entre la conception et la vérification finale. Pour les procédés avancés 45nm et en deçà, l’approche « dessiner puis vérifier » est susceptible de compliquer la convergence car les corrections peuvent altérer les objectifs de conception tels que la surface, le timing et la consommation. La vérification physique en cours de conception ‘In-design’ avance la totalité des vérifications physiques dans la phase de dessin , aidant à faire sortir de l’environnement de conception un layout propre, évitant ainsi des surprises de dernière minute, proche de la mise en fabrication (tape-out).

Des règles spécifiques ou des portions de circuits peuvent être vérifiées incrémentalement, diminuant le temps total de conception. De plus, IC Validator peut trouver et réparer des violations de règles de dessin dans le contexte global du design. Des opérations habituellement réalisées durant la vérification physique, tel que le remplissage métal, peuvent nécessiter des changements additionnels pour obtenir la convergence de timing. Travaillant de concert avec IC Compiler, le flow IC Validator ‘in-design’ réduit considérablement le nombre d’itérations en réalisant le remplissage des couches métal avec la qualité requise pour la fabrication dès la phase de design en prenant le timing en compte.

« Nos clients ont identifié le besoin d’un DRCS/LVS plus rapide pour les procédés technologies avancées, et la nécessité de réaliser la vérification physique plus tôt dans le flow d’implémentation pour limiter les itérations qui peuvent considérablement retarder la mise en fabrication » déclare Antun Domic, senior vice président en charge du groupe Implémentation de Synopsys. « La vérification ‘In-design’ avec IC Validator, combinée avec sa précision et la prise en compte efficace des règles de design toujours plus complexes, raccourcira considérablement le cycle de vérification physique de nos clients. »