Ce développement est issu d’un programme de recherche financé avec le soutien de l’Union Européenne, de la Région Bretagne, et des collectivités locales (département et métropole), ayant pour objectif de renforcer les capacités techniques de l’ENSTA Bretagne dans le domaine de la cyber défense.

Ce développement est issu d’un programme de recherche financé avec le soutien de l’Union Européenne, de la Région Bretagne, et des collectivités locales (département et métropole), ayant pour objectif de renforcer les capacités techniques de l’ENSTA Bretagne dans le domaine de la cyber défense.

Un FPGA embarqué est un IP programmable intégré dans des systèmes sur puce (SoC) ou des circuits intégrés sur mesure (ASIC). La technologie eFPGA fait de plus en plus d’adeptes parmi les architectes système qui doivent faire face à des exigences de marché en évolution constante et à des circuits intégrés qui deviennent de plus en plus complexes et coûteux à développer. « L’ajout de la fonctionnalité eFPGA aux conceptions ASIC apporte la flexibilité et les performances de la logique programmable, à moindre coût, mais avec une puissance, des performances et une latence améliorées », selon Théotime Bollengier, architecte IC à l’ENSTA Bretagne.

Le eFPGA proposé par l’ENSTA Bretagne présente les caractéristiques suivantes :

![]() 3200 Look-Up-Tables (LUT) afin d’implanter toute fonction booléenne à 4 entrées

3200 Look-Up-Tables (LUT) afin d’implanter toute fonction booléenne à 4 entrées

![]() Structure à base de cellules standards pour une génération automatisée à partir d’une description RTL

Structure à base de cellules standards pour une génération automatisée à partir d’une description RTL

![]() Solution techno-indépendante car basée sur des cellules standard

Solution techno-indépendante car basée sur des cellules standard

![]() Intégration dans un flot de conception RTL standard

Intégration dans un flot de conception RTL standard

![]() Génération et programmation effectuées grâce à l’outil ArGen de l’ENSTA Bretagne

Génération et programmation effectuées grâce à l’outil ArGen de l’ENSTA Bretagne

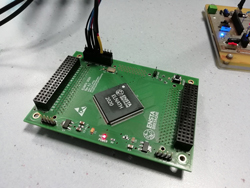

L’entreprise IC’Alps s’est vu confier la responsabilité de l’implémentation et du prototypage sur silicium, tous deux nécessaires pour faire un premier démonstrateur de la technologie ENSTA. La société était en charge de la définition de l’ASIC, de la sélection du procédé de fabrication, de la conception (synthèse, floorplan, placement & routage), de la stratégie de test, des simulations post-layout et des vérifications avant le lancement en fabrication. IC’Alps a également pris en charge la gestion de la chaîne d’approvisionnement, incluant la sélection des partenaires, la fabrication de la puce et son assemblage en boitier.

« Cet ASIC réalisé pour l’ENSTA Bretagne est une démonstration de notre expertise en matière d’implémentation physique et de notre capacité à mettre en place et à gérer une chaîne d’approvisionnement complète », a déclaré Jean-Luc Triouleyre, Président d’IC’Alps. « Notre équipe a collaboré avec l’ENSTA-Bretagne dès la spécification de l’ASIC, a respecté ses engagements de délai pour la mise en fabrication et la livraison des puces packagées, et ce dans une période difficile et incertaine liée à la pandémie COVID. Enfin, l’équipe a également démontré son engagement en matière de qualité pour atteindre un silicium bon du premier coup ».

L’approche collaborative d’IC’Alps a permis à l’ENSTA Bretagne de bénéficier d’une grande flexibilité (données d’entrées, flot d’implémentation). La complémentarité entre les deux équipes techniques a été un point clé pour relever le défi d’une disponibilité rapide d’un démonstrateur fonctionnel sur silicium. « Nous sommes heureux de vous annoncer que le premier démonstrateur en technologie TSMC 55 nm ULP est de retour de fabrication, validé et fonctionnel », ont ajouté Loïc Lagadec et Jean-Christophe Le Lann, tous deux chercheurs à l’ENSTA Bretagne.