![]() Pack de développement FPGA pour Cyclone™ II (Altera®)

Pack de développement FPGA pour Cyclone™ II (Altera®)

![]() Intelligence intégrée grâce au noyau logiciel Nios®

Intelligence intégrée grâce au noyau logiciel Nios®

![]() Robustesse, souplesse et disponibilité à long terme

Robustesse, souplesse et disponibilité à long terme

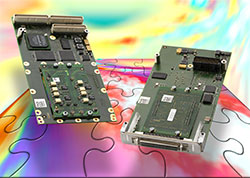

Les deux modules à base de FPGA introduits il y a un an, les PMC P599 et M-Module™ M199, sont désormais accompagnés d’un PMC, le P598 version conduction cooled et d’un module XMC, le P699. Le concept de sous-module universel, USM™, sur lequel s’appuie cette famille d’E/S, implante les fonctionnalités désirées sous forme de coeur IP à l’intérieur du FPGA de la carte mezzanine, tandis que les drivers de ligne sont implantés dans le sous-module.

Le concept USM™ permet de réaliser des combinaisons inhabituelles d’E/S dans un espace restreint à moindre coût. Pour ce faire, le XMC P699 est équipé d’un FPGA Cyclone™ III à 24 624 LE, et le PMC P598 refroidi par conduction d’un Cyclone™ II à 33 216 LE. Les P699 et P598 ont des fonctions spécifiques en fonction du coeur IP choisi. La fonction peut être changée à tout moment en utilisant un coeur IP différent, sans aucune modification matérielle. Les drivers de ligne correspondants sont implantés dans un sous-module conçu spécifiquement pour chaque application, et qui est branché sur le XMC ou le PMC. Le module dispose aussi de 32 Mo de mémoire SDRAM DDR2, et de jusqu’à 4 Mo de mémoire flash nécessaire lors de l’utilisation du cœur CPU NIOS

Au delà cette flexibilité, l’utilisation de coeurs IP offre aussi l’avantage d’une pérennité sans précédent.

Grâce à un pack de développement USM™ complet, l’utilisateur peut facilement et rapidement créer ses fonctions d’E/S. Le pack comprend un PMC avec un sous-module USM™, du matériel de test et un module FPGA à CPU Nios®, un contrôleur mémoire, une connexion au PMC, des passerelles Avalon®/Wishbone et une documentation détaillée. Pour le développement de coeurs IP sur bus standard Wishbone, on utilisera l’outil Wishbone Bus Maker MEN inclus. Pour pouvoir utiliser le coeur Nios® et développer des coeurs IP sur bus Avalon®, vous avez également besoin de l’environnement de conception Quartus® II d’Altera® incluant SOPC builder.

Pour les utilisateurs préférant les produits prêts à l’emploi, MEN propose aussi la conception et l’implantation de coeurs IP, ainsi que la conception de sous-modules USM™