Le CIEN, fusion du Forum de l’électronique et de RF&Hyper Europe, offre une nouvelle dynamique et un nouvel évènement pour la filière électronique et numérique. Mêlant salon professionnel, conférences et animations techniques opérationnelles, conférences de haut niveau sur les marchés du futur.

ASTER vous attend de 9h00 à 18h00, les 1, 2 et 3 juin 2010, Porte de Versailles, Pavillon 7.1, Stand H31. Des démonstrations des nouveautés seront organisées tout au long de la journée.

TestWay – Analyse combinée mécanique et électrique TestWay, la référence mondiale en analyse de couverture de test, permet à ses utilisateurs de quantifier et qualifier la couverture pour de nombreux équipements de test et d’inspection. Une nouvelle fonctionnalité a été introduite pour optimiser les accès physiques, tout en maintenant une couverture de test maximale.

TestWay – Analyse combinée mécanique et électrique TestWay, la référence mondiale en analyse de couverture de test, permet à ses utilisateurs de quantifier et qualifier la couverture pour de nombreux équipements de test et d’inspection. Une nouvelle fonctionnalité a été introduite pour optimiser les accès physiques, tout en maintenant une couverture de test maximale.

“Probe Analyzer” est un logiciel interactif, piloté par des règles d’analyse mécanique spécifiquement conçues pour assister les ingénieurs de conception et les développeurs de test. Il identifie rapidement les surfaces de cuivre utilisables comme accès physiques. Cette information est combinée avec les capacités de mesure de l’équipement ciblé, pour estimer la couverture pour le test ICT ou FPT. TestWay génère un rapport détaillé d’accessibilité physique précisant la position du point de test retenue, ou les violations des règles interdisant l’utilisation de certains points.

Une analyse de couverture de test très sophistiquée permet de décrire la ligne de production en combinant les tests ICT (In-Circuit Test) ou FPT (Flying Probe Test) avec des techniques d’inspection ou de test telles que AOI (Automated Optical Inspection), AXI (Automated X-Ray Inspection), BST (Boundary-Scan Test) ou test fonctionnel. TestWay estime la couverture avant le développement des tests en identifiant les zones où l’efficacité est limitée compte tenu de la violation de règles DfT électriques.

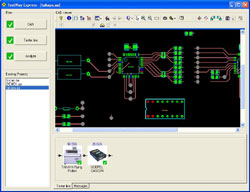

Génération de la documentation de fabrication QuadView est un ensemble de visualisateurs spécialisés pour l’industrie électronique. A partir des données CAO d’une carte électronique, il affiche simultanément le schéma d’implantation et le schéma électrique.

Afin de faire face aux besoins des industriels en charge de l’assemblage des cartes électroniques, ASTER a décidé de révolutionner la génération de la documentation. Le nouveau logiciel QuadView-Documentor intègre les fonctions spécialisées de QuadView dans l’interface utilisateur d’un logiciel de traitement de texte. La barre d’outils spécialisés vient s’insérer dans l’interface du standard mondial Microsoft-Word. Elle permet d’activer toutes les fonctions de visualisation, de colorisation, de recherche, de sélection…

Avec cette architecture innovante, les efforts d’ingénierie sont considérablement réduits lors de la création des gammes de fabrication, des instructions de travail et des aides visuelles.

En quelques clics, les données CAO sont analysées et mises en forme pour une utilisation immédiate sur les lignes de fabrication, soit sous forme de dossier « papier », soir en format HTML, pour être visualisées sur n’importe quel navigateur Internet du marché.

JTAG : Diminuer vos temps de programmation.

Depuis son introduction dans les années 1990, le test Boundary-Scan s’appuyant sur la norme JTAG IEEE1149.1 est devenu un outil essentiel pour tester les cartes électroniques dans les phases de prototypage, de production et de maintenance. Le niveau d’intégration et le manque d’accessibilité ont favorisé le succès de cette technique de test. La société GOEPEL représentée par ASTER depuis 15 ans, lance la technologie VARIOTAP. Celle-ci permet de combiner les ressources d’émulation avec le test Boundary-Scan ouvrant ainsi de nouvelles perspectives en repoussant les limites du test Boundary-Scan traditionnel. La capacité des composants programmables ne cesse d’augmenter ce qui provoque des temps de programmation de plus en plus conséquents. L’augmentation de la fréquence d’horloge n’est plus suffisante pour assurer des temps de programmation raisonnables. La technique d’émulation est issue des outils de « Debug logiciel » qui permettent de stimuler directement le cœur du processeur ou du micro-contrôleur. En fusionnant les deux techniques, la programmation est réalisée à la fréquence de fonctionnement réelle de la carte. C’est une réduction pouvant atteindre 80% du temps de programmation !