A lire dans le N°116 d’Electronique Mag http://www.electronique-mag.net/pag...

![]() Cadence Design Systems, Inc. annonce sous la référence Cadence® Tensilica® Vision C5, le premier coeur de DSP de l’industrie, autonome pour les réseaux de neurones. Ce DSP est conçu pour répondre de façon optimale aux applications de vision, radar/lidar et fusion des données collectées par des capteurs associées à des réseaux neuronaux nécessitant de hautes exigences de calcul. Destiné aux marchés de l’automobile, de la surveillance, des drones et des communications mobiles/portables, le processeur Vision C5 dispose d’une capacité de calcul de 1 TMAC1/sec qui permet d’exécuter toutes les tâches de calcul des réseaux de neurones.

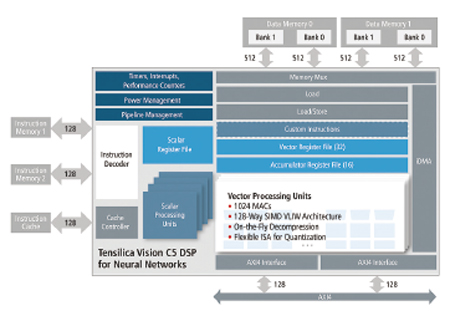

Cadence Design Systems, Inc. annonce sous la référence Cadence® Tensilica® Vision C5, le premier coeur de DSP de l’industrie, autonome pour les réseaux de neurones. Ce DSP est conçu pour répondre de façon optimale aux applications de vision, radar/lidar et fusion des données collectées par des capteurs associées à des réseaux neuronaux nécessitant de hautes exigences de calcul. Destiné aux marchés de l’automobile, de la surveillance, des drones et des communications mobiles/portables, le processeur Vision C5 dispose d’une capacité de calcul de 1 TMAC1/sec qui permet d’exécuter toutes les tâches de calcul des réseaux de neurones.

À mesure que les réseaux de neurones deviennent plus complexes, les exigences de calcul augmentent rapidement. Parallèlement, les architectures de réseaux de neurones évoluent régulièrement, de nouveaux réseaux font constamment leur apparition tandis qu’émergent de nouvelles applications et de nouveaux marchés. Ces tendances impliquent l’utilisation d’une solution de traitement pour réseaux de neurones à la fois polyvalente, performante, adaptée aux systèmes embarqués et économe en énergie tout en conjuguant un haut niveau de programmation, une flexibilité à l’épreuve du futur et des risques réduits.

Les systèmes de visualisation par caméra utilisés dans les véhicules automobiles, les drones et les systèmes de sécurité nécessitent deux types fondamentaux de calculs optimisés pour la vision. Tout d’abord, les données captées par la caméra sont enrichies par des algorithmes de calcul traditionnellement utilisés dans les applications de photographie et d’imagerie. Deuxièmement, les algorithmes de reconnaissance à base de réseaux de neurones assurent la détection et la reconnaissance des objets. Les accélérateurs de réseaux de neurones actuellement disponibles sont des accélérateurs matériels associés aux DSP d’imagerie, le code des réseaux de neurones étant utilisé pour exécuter certaines couches réseau sur le DSP tout en « délestant » la gestion des couches de convolution vers l’accélérateur — une combinaison peu performante qui consomme de l’énergie de façon inutile.

Architecturé sous la forme d’un DSP dédié et optimisé pour les réseaux de neurones, le processeur Vision C5 accélère non seulement les fonctions de convolution, mais également toutes les couches de calcul des réseaux de neurones (couche de convolution (CONV), couche entièrement connectée (FC), couche de pooling (POOL) et couche de normalisation). Cette technique permet au DSP principal chargé des tâches de vision/imagerie d’exécuter des applications d’amélioration graphique séparément, tandis que le DSP Vision C5 gère les tâches d’inférence. En éliminant les mouvements de données externes entre le DSP pour réseaux de neurones et le DSP principal chargé des tâches de vision/imagerie, le processeur Vision C5 consomme moins d’énergie que les accélérateurs concurrents tout en représentant un modèle simple de programmation monoprocesseur pour réseaux de neurones.

« Bon nombre de nos clients se trouvent dans la position délicate où ils doivent aujourd’hui choisir une plateforme d’inférence pour réseaux de neurones utilisée avec un produit qui ne sera peut-être pas disponible avant quelques années », a déclaré Steve Roddy, directeur du groupe Tensilica chez Cadence. « D’une part, les processeurs pour réseaux de neurones destinés à des systèmes embarqués actifs en permanence doivent consommer moins d’énergie, mais aussi faire preuve de rapidité à chaque image, tout en étant flexible et parés pour le futur. Toutes les alternatives actuellement disponibles imposent des compromis indésirables, et il s’est avéré qu’une solution nouvelle était nécessaire. Nous avons conçu le processeur Vision C5 comme un DSP pour réseaux de neurones polyvalent à la fois très souple, facile à intégrer, et qui affiche une consommation d’énergie inférieure aux accélérateurs CNN, aux processeurs (CPU) et autres processeurs graphiques (CPU). »

« Les applications à apprentissage profond (deep learning) utilisées par les appareils du monde réel sont énormes et très variées, elles impliquent d’importantes capacités de calcul », a déclaré Jeff Bier, fondateur de l’Embedded Vision Alliance. « Des processeurs programmables spécialisés tels que le DSP Vision C5 permettent de déployer du « deep learning » dans des produits où la consommation d’énergie et le coût sont des paramètres critiques. »

Le processeur Vision C5 de Cadence assure aux réseaux de neurones des performances de premier plan dans un moteur intégré :

![]() Une capacité de calcul de 1 TMAC/sec (soit 4 fois plus que le DSP Vision P6) sur une surface de silicium inférieure à 1 mm2 qui assure une puissance de calcul très élevée aux noyaux de deep learning ;

Une capacité de calcul de 1 TMAC/sec (soit 4 fois plus que le DSP Vision P6) sur une surface de silicium inférieure à 1 mm2 qui assure une puissance de calcul très élevée aux noyaux de deep learning ;

![]() 1024 8 bits MAC ou 512 16 bits MAC pour des performances exceptionnelles pour des résolutions 8 et 16 bits ;

1024 8 bits MAC ou 512 16 bits MAC pour des performances exceptionnelles pour des résolutions 8 et 16 bits ;

![]() Architecture SIMD (Single Instruction on Multiple Data) VLIW (Very Long Instruction Word) avec mode SIMD 8 bits/128 canaux ou 16 bits/64 canaux ;

Architecture SIMD (Single Instruction on Multiple Data) VLIW (Very Long Instruction Word) avec mode SIMD 8 bits/128 canaux ou 16 bits/64 canaux ;

![]() Architecture pour circuit multicoeurs, ce qui permet de réaliser une solution multi-TeraMAC dans un encombrement réduit ;

Architecture pour circuit multicoeurs, ce qui permet de réaliser une solution multi-TeraMAC dans un encombrement réduit ;

![]() Interface iDMA et AXI4 intégrée ;

Interface iDMA et AXI4 intégrée ;

![]() Utilise les même outils logiciels éprouvé pour les DSP Vision P5 et P6 ;

Utilise les même outils logiciels éprouvé pour les DSP Vision P5 et P6 ;

![]() Par rapport aux processeurs graphiques du commerce, le DSP Vision C5 est jusqu’à 6 fois plus rapide selon l’étude comparative AlexNet CNN, et jusqu’à 9 fois plus rapide selon l’Inception V3 CNN.

Par rapport aux processeurs graphiques du commerce, le DSP Vision C5 est jusqu’à 6 fois plus rapide selon l’étude comparative AlexNet CNN, et jusqu’à 9 fois plus rapide selon l’Inception V3 CNN.

Le processeur Vision C5 est une solution flexible parée pour le futur qui prend en charge différentes tailles de noyau, profondeurs et dimensions d’entrée. Il est également compatible avec différents degrés de compression/ décompression. Il permet l’ajout de nouvelles couches à mesure de leur évolution, contrastant avec les accélérateurs matériels qui reste une solution rigide en raison d’une capacité de reprogrammation limitée.

Le processeur Vision C5 DSP est fourni avec l’outil de mappage pour réseaux de neurones de Cadence (Caffe et TensorFlow). Tout réseau neuronal est mappé en un code exécutable et hautement optimisé pour le processeur Vision C5, en s’appuyant sur un ensemble complet de fonctions issues de bibliothèques de réseaux de neurones optimisées manuellement.

Des contrats sont déjà en cours avec certains clients. Les clients intéressés par le processeur Vision C5 sont invités à contacter leur représentant Cadence.