Synopsys, Inc. (NASDAQ : SNPS), un leader du logiciel et de l’IP pour la conception, la vérification et la fabrication de semi-conducteurs, annonce aujourd’hui sa solution de synthèse de haut niveau, Synphony HLS, qui supporte le langage M* et la synthèse basée sur les modèles, permettant un gain de productivité atteignant d’un rapport 10 comparé aux méthodologies RTL, pour la conception et la vérification des ASIC et FPGA dans les applications communications et multimédias. Synphony HLS crée un RTL optimisé pour l’implémentation ASIC et FPGA, l’exploration d’architectures et le prototypage rapide. De plus, Synphony HLS complète le flow C/C++, en générant des modèles C pour la validation système et le développement précoce de logiciels sur une plateforme virtuelle. Synphony HLS est intégré avec : Synopsys Design Compiler(R), Synplify(R) Premier, Confirma(TM), VCS(R), System Studio et Innovator pour fournir le flot le plus complet de prototypage, de vérification et d’implémentation, de l’algorithme au Silicium.

La solution Synphony HLS augmente significativement la productivité par rapport aux méthodes traditionnelles en fournissant :

![]() Un flot automatique du M au RTL optimisé

Un flot automatique du M au RTL optimisé

![]() Une synthèse d’architectures RTL optimisées pour les ASIC et FPGA

Une synthèse d’architectures RTL optimisées pour les ASIC et FPGA

![]() Une méthodologie de prototypage rapide pour une validation précoce des algorithmes

Une méthodologie de prototypage rapide pour une validation précoce des algorithmes

![]() La génération de modèles C pour un développement précoce du logiciel et la

validation rapide du système

La génération de modèles C pour un développement précoce du logiciel et la

validation rapide du système

![]() Une vérification unifiée pour différents flots dont le prototypage et l’implémentation ASIC

Une vérification unifiée pour différents flots dont le prototypage et l’implémentation ASIC

« La solution Synphony HLS changera fondamentalement la façon dont les FPGA et ASIC seront utilisés pour la validation système et le développement du software embarqué » déclare Richard Cagley, Ph.D., développeur d’algorithmes chez Toyon Research Corporation. “Les méthodologies HLS mobilisaient d’importantes ressources de développement hardware pour traduire nos algorithmes en RTL en vue de leur implémentation sur Silicium, FPGA ou ASIC. Synphony HLS me permet d’utiliser le langage M aussi bien pour la simulation de haut niveau que pour la production de code ; ce qui signifie que je peux maintenant aller de la simulation directement vers le hardware en quelques heures ou jours, non plus en mois ou années. Cela à un impact important sur notre productivité, nos plannings et la qualité des produits basés sur nos algorithmes. »

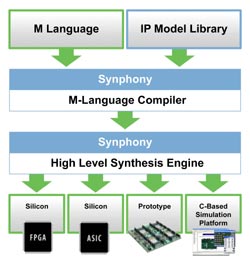

Un flot automatique du langage M et de l’IP de haut niveau, vers le RTL optimisé Le M-langage de Mathworks a été largement adopté pour l’exploration et la conception d’algorithmes parce qu’il permet l’expression concise du comportement à un niveau d’abstraction extrêmement élevé. Pour l’implémentation et la vérification, ces modèles M sont traditionnellement recodés manuellement et revérifiés au niveau RTL et parfois C/C++. A la différence de ces flots inefficaces et source d’erreurs, Synphony HLS crée directement du RTL implémentable et des modèles C à partir du code M de très haut niveau et des modèles de la bibliothèque d’IP optimisés de Synphony HLS. Le moteur de synthèse génère des architectures RTL optimisée pour atteindre les objectifs de surface, vitesse et consommation. Synphony HLS permet aux concepteurs de rester dans leur langage préféré de modélisations des algorithmes, il élimine le recodage et accélère la validation système.

Un flot automatique du langage M et de l’IP de haut niveau, vers le RTL optimisé Le M-langage de Mathworks a été largement adopté pour l’exploration et la conception d’algorithmes parce qu’il permet l’expression concise du comportement à un niveau d’abstraction extrêmement élevé. Pour l’implémentation et la vérification, ces modèles M sont traditionnellement recodés manuellement et revérifiés au niveau RTL et parfois C/C++. A la différence de ces flots inefficaces et source d’erreurs, Synphony HLS crée directement du RTL implémentable et des modèles C à partir du code M de très haut niveau et des modèles de la bibliothèque d’IP optimisés de Synphony HLS. Le moteur de synthèse génère des architectures RTL optimisée pour atteindre les objectifs de surface, vitesse et consommation. Synphony HLS permet aux concepteurs de rester dans leur langage préféré de modélisations des algorithmes, il élimine le recodage et accélère la validation système.

Synthèse de haut niveau depuis un modèle unique Le moteur de Synphony HLS synthétise des architectures optimisées pour les ASIC, les FPGA, le prototypage rapide et les plateformes virtuelles, tout en maintenant une vérification cohérente à toutes les étapes du flot d’implémentation. A partir des objectifs spécifiés par l’utilisateur et des contraintes architecturales, le moteur HLS optimise à de multiples niveaux, pipe-lines, scheduling et binding, à travers la hiérarchie et par delà les frontières entre modèles, M ou IP.

Synphony HLS pour la conception d’ASIC

Synphony HLS intègre un nouvel estimateur de timing, qui utilise Design Compiler pour déterminer les timings précis nécessaires pour la génération automatique des pipe-lines et la convergence de timing dans une technologie ASIC donnée.

Synphony HLS pour la conception de FPGA

Synphony HLS intègre des optimisations de timing avancée et des optimisations spécifiques à chaque famille d’un large choix de FPGA d’Actel, Altera, Lattice et Xilinx. Cela inclut l’utilisation des multiplieurs hardware, mémoires, registres et autres ressources matérielles avancées disponibles dans les FPGA modernes.

Synphony HLS pour le prototypage rapide

Avec Synphony HLS et Confirma, la solution Synopsys de prototypage rapide à la pointe de la technologie, les équipes de conception peuvent créer rapidement un prototype pré-Silicium et commencer la validation des algorithmes et le développement du logiciel beaucoup plus tôt durant le cycle de conception.

Une sortie C pour un développement logiciel précoce et une validation système plus rapide Synphony HLS complète le flot C/C++ d’implémentation, de vérification et de développement du logiciel embarqué, en générant le Modèle C. Synphony HLS génère des modèles virgule fixe en ANSI-C qui peuvent être utilisés par une variété d’environnements de simulations systèmes et de plateformes virtuelles comme Synopsys Innovator, System Studio, VCS et SystemC. Il permet de commencer beaucoup plus tôt la validation et à la vérification basée sur le C.

“Jusqu’à maintenant il n’y avait pas de solutions pour dériver à partir du très populaire langage M, un flot d’implémentation et un flot de vérification cohérent à travers les différents niveaux d’abstraction, ” dit Gary Meyers, vice président et général manager du Synplicity Business Group chez Synopsys. “Avec Synphony HLS, nous fournissons un chemin plus rapide et plus fiable pour la validation système et software que ce que propose les solutions concurrentes. En combinant les technologies de pointe de Synopsys pour le prototypage système et la vérification assistée par hardware, les équipes de conception peuvent concevoir et vérifier plus rapidement et plus surement leurs circuits intégrés complexes et leurs logiciels.”

Packaging et disponibilité

Synphony HLS inclut la technologie de synthèse-M, la génération de modèle C, la bibliothèque d’IP de haut niveau Synphony et le moteur Synphony HLS pour les ASIC et les FPGA. Synphony HLS est disponible aujourd’hui pour un nombre limité de clients et sera accessible à tous à la fin de l’année calendaire 2009. Pour plus d’informations visitez le site http://www.synopsys.com/Tools/SLD/A... ou contactez votre commercial Synopsys local.