Linear Technology Corporation présente un convertisseur analogique-numérique (CAN), 80 Méch./s, 16 bits sans perte de code, ne consommant que 89 mW, moins de la moitié de la consommation des produits 16 bits concurrents. Le LTC2259-16 constitue une amélioration, avec compatibilité de brochage avec la famille de CAN LTC2259-14, 14 bits, de faible consommation, en présentant la dissipation la plus petite pour un seul CAN 16 bits à sorties CMOS / LVDS à débit de données double (DDR). En plus de présenter cette faible consommation, le LTC2259-16 intègre deux caractéristiques utiles pour réduire la boucle de retour des signaux numériques, le mode polarité alternée des bits (ABP) et un générateur de données aléatoires de sortie. Ces caractéristiques, associées à une faible consommation, facilite la tâche de conception avec des CAN rapides, dans une grande variété d’applications, comme les caméras de télévision HD, les radars IMO, les testeurs Ethernet, les systèmes de tests portables et de l’instrumentation, les radios numériques et les stations de base pour téléphone cellulaire.

Le signal numérique de retour survient quand l’énergie provenant des sorties du CAN se superpose au signal de la section analogique, ce qui cause des interactions qui se traduisent par des formes de signaux impropres dans le bruit de fond et des parasites dans le spectre de sortie du CAN. Le pire cas se situe à mi-échelle, lorsque toutes les sorties passent de 1 à 0, ou vice versa, générant de forts courants de masse qui reviennent dans l’entrée.

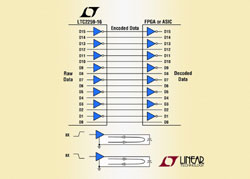

Pour combattre cet effet, le mode propriétaire, à polarité alternée des bits (ABP) du LTC2259-16, inverse tous les bits des lignes impaires avant les tampons de sortie pour égaliser le nombre de 1 et de 0 qui commutent. Cette méthode annule les forts courants de masse qui contribuent au retour des signaux numériques. En plus du mode de polarité alternée des bits, un générateur de données aléatoires de sortie est disponible, en option, pour réduire les interférences provenant des sorties numériques. Ce générateur dissocie la sortie numérique pour réduire la probabilité de présence de codes répétitifs venant en boucle de retour se coupler à l’entrée du CAN, ce qui causerait des fréquences indésirables dans le spectre de sortie. Les deux techniques de réduction du signal de retour numérique permettent d’améliorer la gamme dynamique sans parasites (SFDR) de 10 à 15 dB. Fonctionnant à partir d’une tension analogique de 1,8 V, le LTC2259-16 présente un rapport signal / bruit (SNR) de 73,1 dB et une gamme dynamique exempte de parasites (SFDR) de 88 dB en bande de base. Une gigue de très faible niveau, de 0,17 psefficace ,permet un sous-échantillonnage pour des fréquences FI, avec un niveau de bruit excellent. Le LTC6406 est recommandé en tant que pilote de CAN, rail-à-rail, pour assurer le fonctionnement en AC du LTC2259-16.

Les sorties numériques du LTC2259-16 peuvent être configurées pour des vitesses de conversion compatibles, CMOS, DDR CMOS ou DDR LVDS. Les sorties numériques à débit de données double permettent la transmission des données sur les fronts montant et descendant du signal d’horloge, ce qui divise par deux le nombre de lignes de données nécessaires. Une alimentation de sortie, séparée, permet au signal de sortie CMOS d’avoir une amplitude comprise entre 1,2 V et 1,8 V.

Présenté en un boîtier QFN, 6 mm x 6 mm, le LTC2259-16 comprend un circuit stabilisateur de rapport cyclique de l’horloge, à partir des rapports cycliques différents de 50%, un rythme programmable du signal numérique de sortie, des intensités des sorties LVDS programmables et une terminaison en sortie LVDS optionnelle. Toutes ces caractéristiques contribuent à rendre plus souple la transmission des données entre le CAN et le récepteur de signal numérique.

Le LTC2259-16 rejoint une famille de CAN 12 et 14 bits, compatibles broche à broche, présentant des vitesses d’échantillonnage de 25 Méch./s à 150 Méch./s, et consommant de 35 mW à 149 mW, respectivement. Le LTC2259-16 est en production. Les échantillons et les cartes de démonstration sont disponibles. L’ensemble des produits de la famille se trouve sur http://www.linear.com/ad/highspeedA....

Légende photo : mode polarité alternée des bits sur le LTC2259-16

Résumé des caractéristiques : famille LTC2259-16

• CAN 16 bits sans perte de codes

• SNR : 73,1 dB

• SFDR : 88 dB

• Faible consommation : 89 mW

• Alimentation simple : 1,8 V

• Sorties CMOS, DDR CMOS ou DDR LVDS

• Sélection de la gamme de tensions d’entrée : 1 Vcrête à crête à 2 Vcrête à crête

• Amplificateur échantillonneur / bloqueur pleine puissance à 800 MHz

• En option, générateur de données aléatoires de sortie

• En option, stabilisateur de rapport cyclique de l’horloge

• Modes arrêt et pause

• Configuration pour port série SPI

• Versions 14 bits et 12 bits compatibles broche à broche

• Boîtier QFN de 40 broches, 6 mm x 6 m