![]() Cette nouvelle plateforme réduit les opérations de layout par plus de 3 en technologie FinFET et triple le débit de simulation de Virtuoso ADE. L’utilisation d’algorithmes statistiques avancés réduit les délais d’analyse des variations de conception d’environ 20 %. L’outil Virtuoso ADE Verifier améliore le processus de mise en conformité aux normes en vigueur d’environ 30 %. La plateforme de conception Virtuoso System Design Platform améliorée avec la prise en charge de plusieurs technologies et kits de conception PDK.

Cette nouvelle plateforme réduit les opérations de layout par plus de 3 en technologie FinFET et triple le débit de simulation de Virtuoso ADE. L’utilisation d’algorithmes statistiques avancés réduit les délais d’analyse des variations de conception d’environ 20 %. L’outil Virtuoso ADE Verifier améliore le processus de mise en conformité aux normes en vigueur d’environ 30 %. La plateforme de conception Virtuoso System Design Platform améliorée avec la prise en charge de plusieurs technologies et kits de conception PDK.

Soucieux d’améliorer la productivité des systèmes électroniques et de la conception de circuits intégrés, Cadence Design Systems, Inc. (NASDAQ : CDNS) a apporté des améliorations majeures à sa plateforme de conception de circuits intégrés « custom » Cadence® Virtuoso®. Ces améliorations concernent la quasi-totalité des produits Virtuoso, fournissant aux ingénieurs système un environnement et un écosystème robustes pour concevoir, implémenter et analyser des circuits intégrés, des boîtiers, des cartes électroniques et des systèmes complexes.

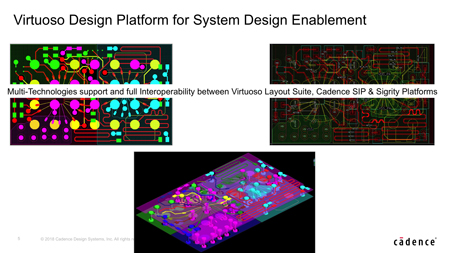

Certaines des principales améliorations apportées à la plateforme Virtuoso 2018 optimisent les capacités de la plateforme primée Virtuoso System Design Platform lancée l’année dernière. La nouvelle version de cette plateforme permet à présent aux ingénieurs système de modifier et d’analyser de manière transparente les systèmes hétérogènes les plus complexes. Par ailleurs, les ingénieurs de différentes disciplines (boitier, photonique, circuits analogiques et RF) peuvent travailler sur une unique plateforme et utiliser la totalité des applications de conception de confiance réunies sur la plateforme Virtuoso.

Au cœur de ce nouvel environnement de conception système se trouve un ensemble de technologies qui permettent de faire de l’édition simultanée bien qu’utilisant plusieurs technologies et kits de conception PDK (Process Design Kit). La plateforme assure en outre une interopérabilité transparente entre Cadence SiP Layout et l‘intégralité des technologies d’analyse Sigrity™, créant ainsi un ensemble complet d’outils « chip to board ».

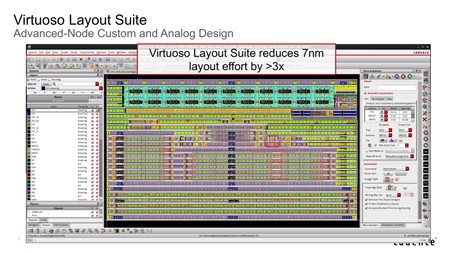

Cette nouvelle mouture de la plateforme Virtuoso intègre des méthodologies pour technologies avancés innovantes, qui accélèrent les projets réalisés dans les nœuds de 22 à 5 nm. En collaborant avec les fondeurs de pointe, ses clients et plusieurs partenaires de son écosystème, Cadence a développé des technologies avancées capables de gérer automatiquement la complexité des processus grâce à des méthodologies innovantes permettant aux ingénieurs de se concentrer sur leurs intentions de conception. En ce qui concerne la conception et l’analyse des circuits, des algorithmes statistiques avancés ciblant spécifiquement les conceptions en technologie FinFET permettent de détecter suffisamment les variations de circuits, ce qui réduit les délais d’analyse des variations de conception d’environ 20 %.

Concernant la conception du layout, un système « multi-grids » unique simplifie les règles de conception complexes des filières 7 nm et 5 nm les plus récentes tout en permettant aux ingénieurs d’augmenter l’utilisation des technologies de placement-routage en vue d’accroître de façon significative la productivité. L’association de ces techniques et des améliorations apportées à la méthodologie avancée divise par plus de 3 les tâches de layout dans les conceptions de production en 7 nm.

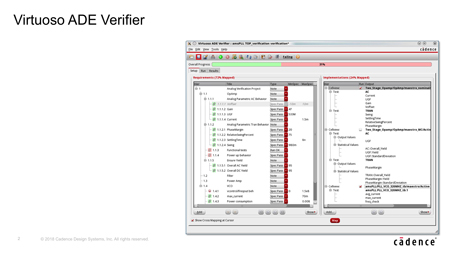

Cadence a apporté plusieurs améliorations pour perfectionner la conception et l’analyse des circuits analogiques.. Le débit de simulation de la suite Cadence® Virtuoso® Analog Design Environment (ADE) est accéléré jusqu’à 3x grâce à une meilleure intégration à l’outil Cadence Spectre® Circuit Simulator, améliorant les vitesses de simulation et donnant accès à des analyses avancées permettant de minimiser les itérations de conception. Des fonctionnalités uniques ont été ajoutées aux capacités de l’outil Virtuoso ADE Verifier afin de centraliser les spécifications électriques multi-domaines, ce qui permet d’accélérer la mise en conformité aux normes en vigueur (ISO 26262, par exemple) d’environ 30 %.

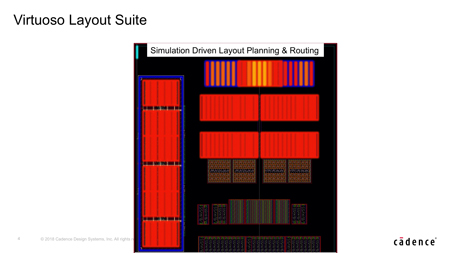

L’environnement Virtuoso Layout évolue d’une configuration de validation électrique (« electrically aware ») vers la première solution de layout pilotée électriquement et par la simulation du marché en utilisant des ensembles uniques de technologies « in-design » pour assurer l’intégrité et optimiser les performances des circuits en cours de conception. Cette nouvelle solution de layout pilotée par la simulation permet de résoudre nombre des problèmes d’électromigration (EM) et d’effets parasites qui pénalisent les circuits critiques et les conceptions en nœuds technologiques avancés. Pour accroître l’automatisation du layout, le nouvel environnement s’enrichit de techniques révolutionnaires de planification et de floorplanning hiérarchique, ainsi que de nouvelles technologies d’automatisation du placement-routage dans le but d’augmenter la productivité et le débit de conception du layout, tout en raccourcissant les délais d’exécution du layout.

Compte tenu de la complexité des circuits intégrés modernes, l’un des principaux défis consiste à répartir les tâches de layout entre les différents concepteurs. La plateforme Virtuoso dispose désormais d’une fonction novatrice d’édition des conceptions concurrentielle et en temps réel, ce qui permet aux concepteurs de répartir les tâches de layout et de procéder à des explorations de simulation (« what-if »). Cette approche est particulièrement utile pour corriger les erreurs de règles de dessin (DRC), la finition des circuits intégrés et le routage manuel.

Selon Cadence, ce nouvel environnement de layout avec routage manuel et automatique piloté électriquement, la possibilité de modifier des designs en temps réel, et les techniques révolutionnaires de planification de la conception, permettront ensemble d’améliorer la productivité jusqu’à 50 %.

« Bosch conçoit des systèmes critiques dont la fiabilité est le principal critère. Nous avons besoin d’outils de CAO électronique grâce auxquels nos ingénieurs peuvent concevoir, analyser et implémenter efficacement des circuits conformes à nos exigences de fiabilité sans pénaliser la productivité globale des concepteurs », a déclaré Göran Jerke, chef de projet EDA, Bosch. « Notre collaboration de longue date avec Cadence a mené à des innovations de premier ordre, tant sur le plan de la vérification électrique « electrically-aware » que de la nouvelle conception de layout pilotée électriquement. »