![]() Comme pour les séries précédentes de processeurs EPYC, l’extension de la disponibilité jusqu’à 5 ans figure sur la feuille de route d’AMD pour les CPU EPYC 7003.

Comme pour les séries précédentes de processeurs EPYC, l’extension de la disponibilité jusqu’à 5 ans figure sur la feuille de route d’AMD pour les CPU EPYC 7003.

L’époque où les processeurs de serveurs haute performance étaient uniquement déployés dans des clusters hyperscalaires, les data centers de grandes entreprises ou le calcul haute performance (HPC) est révolue. Aujourd’hui, ils sont également de plus en plus utilisés dans les serveurs edge et les applications réseau en périphérie. L’augmentation rapide des volumes de données brutes, les temps de réponse courts pour l’Internet tactile en temps réel ainsi que les capacités réseau étendues et les bandes passantes élevées exigent des systèmes edge fournissant une large connectivité et des performances téraflopiques élevées, le tout devant également être adapté aux exigences locales spécifiques. Les cas d’utilisation comprennent le contrôle des lignes de production pour la maintenance prédictive dans les usines intelligentes, l’assurance qualité numérique et les Digital Twins (jumeaux numériques) dans les applications Industrie 4.0, ainsi que les contrôles basés sur l’IA dans les villes intelligentes, les transports intelligents et les stations de base 5G.

Toutes ces applications génèrent d’importants volumes de données qui doivent être traitées avec un temps de latence aussi faible que possible et le plus souvent en temps réel. Cela nécessite une puissance de calcul haute performance là où sont générées les données , car l’envoi de données brutes pour traitement vers le cloud, puis le renvoi des résultats, prendrait tout simplement trop de temps. De plus, l’installation de connexions à large bande suffisamment rapides vers le cloud est souvent impossible dans le cas de sites d’application distants. Il n’est pas non plus possible de garantir une connectivité cloud fiable 24 heures sur 24 et 7 jours sur 7. Les exigences élevées en matière de protection des données et la nécessité de limiter les surfaces d’attaque jouent souvent un rôle important, ce qui oblige à éviter, dans la mesure du possible, de longs transports de données brutes sensibles vers le cloud.

Les serveurs edge sont clairement plus qu’une simple interface entre l’OT et l’IT, et ils sont capables de gérer des tâches aussi exigeantes qu’un petit data center. Ils accroissent l’infrastructure cloud classique, en déplaçant la puissance de calcul vers la périphérie des réseaux et loin des data centers centralisés au profit de clouds partagés, de clouds edge et enfin, de puissants serveurs edge en tant que mini data centers locaux connectés au réseau étendu.

Pour accroitre considérablement ces infrastructures edge, il faut des processeurs serveur dotés de performances flexibles qui englobent les cas d’utilisation locaux les plus divers. Outre une connectivité élevée, des performances en virgule flottante (flops) et une gestion mémoire généreuse pour la virtualisation, il faut également des fonctions de sécurité améliorées et un support embarqué étendu. Les OEM qui fournissent la technologie serveur Edge cruciale ont besoin d’une feuille de route à long terme fiable et d’un support conforme aux normes de l’industrie stable pour leurs systèmes.

Les processeurs AMD EPYC Embedded séries 3000, 7001 et 7002 offrent déjà aux OEM et aux développeurs un portefeuille de performances large et nuancé pour chaque scénario d’application. Les nouveaux CPU EPYC 7003, connus sous le nom de code "Milan", font faire un bond en avant en performance à AMD et l’AMD EPYC 7763 est actuellement le processeur serveur le plus puissant au monde, comme l’attestent de nombreux bancs d’essais CPU serveurs publiés par la prestigieuse SPEC (https://www.spec.org/).

Avec la série EPYC 7003, AMD a introduit les nouveaux coeurs Zen 3 pour ses CPU serveur. Comme les processeurs EPYC 7002, ils sont fabriqués en technologie 7 nm ultra-basse consommation et le principe de conception du SoC avec huit CCD (core complex dies) dans un module multi-puce est conservé. Cependant, la nouvelle conception du coeur Zen 3 permet une augmentation considérable de 19 % du taux d’IPC. Cela signifie qu’un CPU EPYC 7003 peut non seulement exécuter plus d’instructions par cycle (IPC) qu’un CPU Zen 2 de la série EPYC 7002, mais aussi augmenter de manière significative les performances CPU disponibles pour les applications et les calculs exigeants des serveurs edge.

Comme les modèles Rome, les coeurs Zen 3 prennent en charge le multithreading simultané (SMT) avec jusqu’à deux threads par coeur. Cela signifie qu’un processeur doté d’un maximum de 64 coeurs peut traiter jusqu’à 128 threads en parallèle. Dans les nouveaux coeurs Zen 3, AMD a désormais augmenté le nombre de prédictions de branchement possibles par cycle d’horloge et a également réduit les latences résultant de prédictions de branchement incorrectes. De plus, un débit plus élevé d’opérations arithmétiques d’entiers dans Zen 3 signifie que dix opérations peuvent maintenant être traitées par cycle d’horloge, au lieu de sept auparavant.

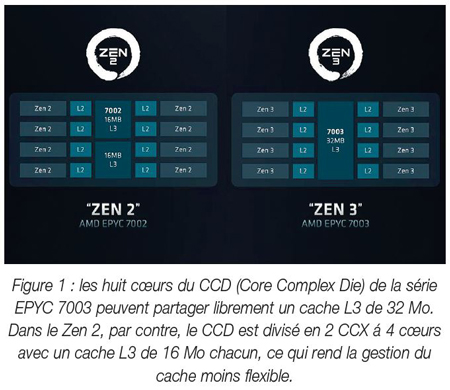

AMD a également amélioré de manière significative le cache L3 de ses processeurs EPYC de troisième génération. Avec jusqu’à 256 Mo par CPU, les processeurs Zen 3 offrent le même cache L3 total que la génération précédente Zen 2, mais ce cache L3 peut désormais être partagé de manière beaucoup plus souple entre les coeurs. Comme sur tous les processeurs AMD basés sur Zen, chaque coeur a accès à son propre cache L3 au sein d’un CCX (core complex). Si nécessaire, un coeur peut utiliser la totalité du cache L3 du CCX. Dans les générations Zen précédentes, AMD combinait 4 coeurs dans un CCX. Dans les processeurs AMD Ryzen 7003, un CCX contient désormais huit coeurs. Le cache L3 par CCX est également doublé, passant de 16 Mo à 32 Mo. Donc, si un coeur a besoin d’une performance élevée pour un seul thread, il peut disposer librement de 32 Mo de cache.

L’amélioration du partage du cache permet de charger de plus grands blocs de données directement dans le cache L3. Mais ce n’est pas tout. Les règles d’extraction et de vidage du cache ont également été optimisées, ce qui permet de réduire la latence de stockage, d’améliorer les performances des programmes grâce à des ensembles de données plus importants et d’augmenter considérablement les performances globales, même en utilisant des machines virtuelles (VM) gourmandes en mémoire. Cela ouvre des possibilités et des cas d’utilisation supplémentaires aux OEM pour déployer leurs serveurs edge.

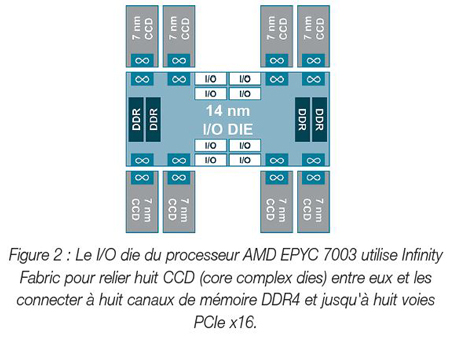

AMD combine en outre jusqu’à huit coeurs Zen en un seul chiplet, appelé "core complex die" (CCD). Ces chiplets sont reliés entre eux par la puissante technologie d’interconnexion Infinity Fabric. Elle relie les coeurs CPU, qui sont organisés en CCD, au contrôleur de mémoire et aux hubs d’E/S et système sur le système-sur-une-puce (SOC). En fonctionnement double socket, elle gère également la communication entre les CPU. Outre l’architecture CPU modulaire, cette interconnexion à haut débit est la raison de la grande évolutivité de tous les processeurs AMD avec microarchitecture Zen.

Le I/O die (IOD), élément central du SoC depuis la génération Zen 2, peut être décrit comme le coeur de l’Infinity Fabric. La vitesse d’horloge de l’Infinity Fabric (FCLK) prend en charge des débits de données allant jusqu’à 1 600 MHz et peut fonctionner en parfaite synchronisation avec les mémoires DIMM DDR4 3 200 MHz (2x1, 600 MHz).

Chaque SoC EPYC 7003 possède huit canaux de mémoire ou contrôleurs mémoire universels (UMC), chaque canal prenant en charge jusqu’à 2 DIMM, de sorte qu’un socket EPYC 7003 peut accueillir un maximum de 16 DIMM, et qu’un seul processeur peut adresser jusqu’à 4 To de mémoire DDR4. Grâce à l’entrelacement de la mémoire CPU, les CPU EPYC 7003 permettent l’utilisation de six canaux de mémoire sans perte de performance, ce qui réduit les coûts de stockage dans des cas d’utilisation ciblés.

De plus, la structure de base de l’IOD dans l’EPYC 7003 n’a pas beaucoup changé. Il est fabriqué en technologie 7nm et dispose de huit liens d’E/S x16 bits ou hubs d’E/S, offrant un choix généreux jusqu’à 128 voies PCIe Gen4 pour connecter des accélérateurs, tels que le nouvel AMD Instinct, ou des SSD. Ils peuvent également être utilisés pour connecter un deuxième SKU EPYC 7003 identique afin de créer un système double socket. Il ne faut plus que 48 liens Infinity Fabric, ce qui laisse jusqu’à 160 voies PCIe dans un système double socket pour les périphériques dédiés, au lieu de 128 précédemment. Un autre avantage des nouveaux CPU EPYC 7003 est la topologie de noeuds NUMA, qui peut être ajustée en modifiant les paramètres du BIOS. Le BIOS peut être configuré pour diviser l’accès à la mémoire dit non uniforme (NUMA) du processeur en deux, quatre ou huit quadrants, chacun ayant son propre domaine NUMA et des canaux de mémoire attribués individuellement et des hubs d’E/S. Une connexion plus rapide au sein d’un domaine NUMA ouvre des possibilités de personnalisation supplémentaires pour les concepteurs de systèmes et les développeurs de programmes.

Comme c’est le cas pour l’ensemble de la famille EPYC, l’EPYC 7003 dispose d’un processeur sécurisé séparé qui fournit une protection supplémentaire contre les tentatives de manipulation. La virtualisation cryptée sécurisée (SEV, depuis l’EPYC 7001) permet le cryptage des VM à l’aide d’une clé unique, qui n’est connue que du processeur sur lequel la VM s’exécute. Ainsi, différentes VMs sur le même CPU EPYC peuvent être séparées les unes des autres de manière sécurisée. L’état crypté SEV (SEVES, depuis EPYC 7002) étend cette fonctionnalité au registre mémoire que l’hyperviseur alloue à la VM, permettant son cryptage par l’activation d’un module supplémentaire, le GHCB (guest hypervisor communication block). Tout cela garantit que l’hyperviseur, même s’il est lui-même corrompu, ne peut jamais lire les données de stockage de la VM puisque le GHCB, qui se trouve entre la VM et l’hyperviseur, envoie toujours du contenu crypté en réponse aux demandes.

Une autre nouvelle fonction de sécurité de la série 7003 d’AMD EPYC est le SEV secure nested paging (SEVSNP). Le SEV-SNP met en oeuvre une série de mesures de sécurité matérielles supplémentaires, par exemple pour empêcher le remappage de la mémoire des VM via un hyperviseur corrompu et pour fournir une meilleure protection contre les attaques par canal latéral, qui posent souvent un risque de sécurité accru dans les serveurs avec accès physique, car il est difficile de les surveiller. Dans l’ensemble, les exigences croissantes en matière de sécurité à la périphérie du réseau et des solutions intégrées sont abordées systématiquement.

Malgré des performances supérieures, le TDP des CPU AMD EPYC 7003 est presque identique à celui de la série 7002. Cela rend les nouveaux processeurs plus efficaces malgré une basse consommation. Par conséquent, il n’est pas non plus nécessaire d’insérer des dispositifs de refroidissement supplémentaires dans des armoires de serveurs déjà étroites. La compatibilité de la conception thermique présente un autre avantage : les serveurs edge existants, basés sur des CPU Rome et montés sur le même socket SP3, sont relativement faciles à mettre à niveau vers le modèle Milan actuel.