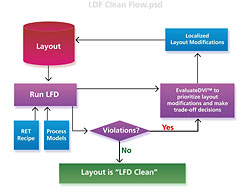

Un article co-rédigé par Infineon Technologies et Chartered Semiconductor Manufacturing rapporte les avantages associés à l’implémentation d’un flot de vérification des procédés lithographiques à l’aide de l’outil Calibre LFD de Mentor Graphics. Calibre LFD permet d’analyser la qualité d’un design "DRC clean" en simulant les effets des variations réelles des procédés lithographiques. Utilisé dès le début du cycle de conception, cet outil permet d’identifier les zones critiques ("hot spots") à l’origine des défauts systématiques. Calibre LFD utilise des modèles de process validés en production fournissant le niveau de précision requis pour apporter des modifications en toute confiance. Depuis mars 2006, Chartered collabore avec Mentor pour fournir un kit de production LFD™.

Cet article intitulé “Hardware Verification of Litho-Friendly Design (LFD) Methodologies [6521-20]” a été présenté en février 2007 lors du symposium SPIE Advanced Lithography. Il a été rédigé par une équipe regroupant des experts d’Infineon et de Chartered (Reinhard März, Kai Peter, Sonja Gröndahl et Klaus Keiner pour Infineon Technologies AG ; Byoung Il Choi, Shyue Fong Quek, Mei Chun Yeo, Nan Shu Chen et Soo Muay Goh pour Chartered).

Les conclusions de l’article se fondent sur une série d’expériences pour prouver la valeur de la vérification physique basée sur des modèles LFD associée à un design traditionnel basé sur des règles dans les géométries 65 nm et moins. Ces expériences comprennent des vérifications lithographiques telles que la largeur minimum (Pinching), l’espace minimum (Bridging), le chevauchement minimum et l’index de variabilité des procédés. Les mesures physiques réalisées sur des tranches de silicium réelles avec des variations contrôlées des paramètres de dose et de focus se sont avérées correspondre aux résultats des simulations LFD. Les expériences ont été conduites sur une bibliothèque de cellules standard Infineon dans l’unité de production Fab 7 de Chartered.

“Il était important de prouver la valeur des capacités de simulation lithographique basées sur des modèles en comparant des résultats simulés à des mesures réalisées sur des matrices de test réelles gravées en 65 nm”, explique Walter Ng, directeur senior des alliances plate-forme de Chartered. “Cette expérience conduite sur la bibliothèque de cellules standard d’Infineon montre qu’un flot LFD hautement précis pour notre process 65nm peut induire des avantages substantiels pour nos clients.”

L’article du SPIE conclut que la seule conformité DRC ne suffit pas à éviter les hot spots susceptibles d’affecter le rendement à 65 nm et moins. Les chercheurs se sont également rendus compte que la majorité des problèmes peuvent être attribués à un petit nombre de cellules, ce qui suggère que la classification d’un nombre relativement petit de problèmes de layout par gravité et par impact sur le rendement peut entraîner une nette amélioration.