Cette solution améliore jusqu’à un facteur 7 les cycles d’analyse temporelle et jusqu’a un facteur 4 la clôture temporelle des designs avec un processeur huit cœurs.

« Nous avons utilisé la nouvelle technologie d’analyse et d’optimisation d’Olympus-SoC pour la conception de notre circuit EMMA extrêmement complexe doté de plus de 30 millions de portes, quatre modes et quatre "corners", une horloge principale à 200 MHz et plus de 150 horloges dérivées », déclare M. Masao Hirasawa, directeur général de la division Digital Consumer LSI de NEC Electronics Corporation. « La fameuse plate-forme EMMA est spécifiquement conçue pour offrir polyvalence et performances aux applications audiovisuelles numériques (décodeurs, TV, enregistreurs de DVD, etc.) grâce à une technologie de traitement des signaux MPEG. Notre principal défi consistait à réussir la clôture temporelle du design dans un délai très court. Nous avons été impressionnés par les performances de la nouvelle solution, puisque nous avons pu réduire l’étape de clôture d’un facteur quatre. Nous sommes toujours très satisfaits des performances globales et des améliorations de productivité obtenues avec Olympus-SoC dans notre flot de conception. »

« La clôture temporelle rapide des designs SoC en 65, 45 et 40 nanomètres est extrêmement importante pour notre compétitivité. Par conséquent, nous recherchons sans cesse la meilleure technologie pour respecter des délais de commercialisation toujours plus courts », poursuit Shoji Ichino, directeur général de la division Technology Development chez Fujitsu Microelectronics Limited. « Le système de placement-routage Olympus-SoC est déjà intégré au kit Reference Design Flow (RDF) que nous utilisons dans de nombreux projets pour régler rapidement les problèmes complexes des designs à modes et "corners" multiples (MCMM, Multi-Corner Multi-Mode). Aujourd’hui, le nouveau moteur temporel Olympus-SoC totalement parallélisé se traduit par une nette accélération de la phase de finalisation des designs, car il bénéficie pleinement des avantages des processeurs multicœurs les plus sophistiqués. »

« La clôture temporelle rapide des designs SoC en 65, 45 et 40 nanomètres est extrêmement importante pour notre compétitivité. Par conséquent, nous recherchons sans cesse la meilleure technologie pour respecter des délais de commercialisation toujours plus courts », poursuit Shoji Ichino, directeur général de la division Technology Development chez Fujitsu Microelectronics Limited. « Le système de placement-routage Olympus-SoC est déjà intégré au kit Reference Design Flow (RDF) que nous utilisons dans de nombreux projets pour régler rapidement les problèmes complexes des designs à modes et "corners" multiples (MCMM, Multi-Corner Multi-Mode). Aujourd’hui, le nouveau moteur temporel Olympus-SoC totalement parallélisé se traduit par une nette accélération de la phase de finalisation des designs, car il bénéficie pleinement des avantages des processeurs multicœurs les plus sophistiqués. »

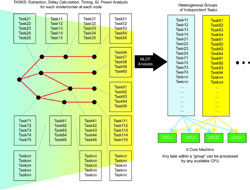

Traitement multicœur : réduction du temps de clôture du design Les tout nouveaux circuits intégrés (CI) exigent une puissance de traitement toujours plus grande pour permettre l’implémentation physique dans les délais impartis. La taille des circuits continue à augmenter au rythme énoncé par la loi de Moore, tandis que les problèmes de variabilité de la fabrication et d’intégrité du signal viennent encore compliquer la situation car ils nécessitent la finalisation de nombreux modes et »corners ». Le meilleur moyen d’accélérer le cycle consiste à appliquer toute la puissance des processeurs multicœurs à l’aspect le plus lourd du flot, à savoir les tâches d’analyse et d’optimisation du timing. En revanche, les architectures traditionnelles de placement-routage ne peuvent pas utiliser toutes les possibilités des processeurs multicœurs dans le noyau de leur moteur temporel, ce qui limite gravement leur évolutivité sur les plates-formes multicœurs.

Le système de placement-routage Olympus-SoC relève ce défi avec une combinaison de multiples technologies désignées « parallélisme orienté tâche ». La technologie de parallélisme orienté tâche développée par Mentor est une technique de discrétisation fine, sans verrouillage qui, pour la première fois, permet la parallélisation des tâches d’analyse et d’optimisation les plus lourdes au sein du noyau temporel du placement-routage. Grâce à une structure de données compacte permettant un nombre illimité de graphiques virtuels de timing, le système Olympus-SoC est par nature performant pour l’analyse MCMM complexe. Pour une utilisation optimale des processeurs multicœurs, le système Olympus-SoC emploie une analyse sophistiquée des flux de données qui permet l’exécution de diverses tâches d’analyse (extraction de parasites, délai, intégrité de signal (SI) MCMM, timing et puissance) en parallèle sur de nombreux processeurs sans les frais de verrouillage et de synchronisation inhérents aux architectures traditionnelles. De plus, il détermine automatiquement la stratégie optimale de partitionnement et de parallélisation à grain fin/grossier adaptée à chaque CI afin de garantir la meilleure qualité de résultats (QoR) et le meilleur temps de cycle (TAT) pour une implantation physique spécifique. Ainsi, le système Olympus-SoC évolue de façon linéaire au fur et à mesure de l’ajout de processeurs, ce qui permet aux clients de finir à temps les designs les plus complexes.

« Les sociétés les plus prestigieuses se tournent de plus en plus vers la solution Olympus-SoC car elle est associée aux meilleurs résultats et aux délais de conception les plus courts », conclut Joe Sawicki, vice-président et directeur général de la division design-to-silicon de Mentor Graphics. « Les autres outils de placement-routage se vantent de gérer le multithread et le multitâche. En revanche, aucun ne dispose d’un moteur d’analyse temporel parallèle pour accélérer l’analyse et l’optimisation MCMM, facteurs qui, au final, déterminent le temps global de finalisation du design. Les succès obtenus sur des produits SoC haut de gamme montrent la différence de Mentor et expliquent pourquoi les clients adoptent massivement notre solution. »