Pendant une bonne trentaine d’années, j’ai participé à de nombreux projets. J’ai conçu seul ou en équipe un grand nombre de produits, en passant par la totalité des postes nécessaires à cette activité, du câblage à l’ingénieur d’affaire en passant par la conception électronique, la programmation et, bien sûr, la conception de circuits imprimés. J’ai travaillé dans de petites entreprises et dans de grands groupes, comme prestataire ou employé, technicien ou ingénieur, ou encore chef de projet.

J’y ai gagné une expérience importante sur de nombreux sujets, mais surtout des convictions inébranlables sur l’importance de la méthodologie à mettre en place, à pratiquer et à améliorer pour toute activité. Je ne suis pas un acharné des normes ISO9000 ou CMMI, mais il faut bien avouer qu’un peu d’organisation et de méthode aide beaucoup à réaliser un projet.

Donc, plutôt que d’écrire le " Nième " manuel qualité, j’ai essayé de reprendre ici quelques idées simples et utiles pour ce qui concerne la conception d’un circuit imprimé destiné à recevoir des composants "rapides". Beaucoup de celles-ci s’appliquent sur tous les projets, bien sûr.

Faire une revue de schémas

Je n’ai jamais compris comment il était possible d’implanter correctement une carte électronique, aussi simple soit-elle, sans en comprendre le fonctionnement. Par exemple, les alimentations à découpage sont omniprésentes sur nos PCB. Lorsqu’elles doivent délivrer une puissance significative (Et quelques watts suffisent à générer moult problèmes), il est important de bien comprendre où sont les points critiques ne serait-ce que pour dimensionner correctement les conducteurs et éviter les diaphonies entre signaux faibles et courants importants.

Les impératifs de fonctionnement

des lignes de transmission

différentielles

représentent une difficulté

supplémentaire. Les impédances

de ces lignes sont

critiques, et doivent être calculées

avec soin sous peine

de voir les dispositifs ne pas

fonctionner correctement.

Tous les fabricants de silicium

proposent des cartes

d’évaluation, et de nombreux

conseils d’implantation.

Mais dans la pratique, il est souvent impossible de

suivre ces règles en raison de problèmes d’encombrement

par exemple, ou parce que le concepteur des schémas

aura tout bonnement détourné un composant de sa

fonction première pour créer quelque chose de neuf.

Tous les fabricants de silicium

proposent des cartes

d’évaluation, et de nombreux

conseils d’implantation.

Mais dans la pratique, il est souvent impossible de

suivre ces règles en raison de problèmes d’encombrement

par exemple, ou parce que le concepteur des schémas

aura tout bonnement détourné un composant de sa

fonction première pour créer quelque chose de neuf.

Bref, lors de la revue de schémas, chaque partie sera analysée et expliquée clairement, en mettant en avant les points critiques, et surtout sans édulcorer les "évidences" qui sont trop souvent évidentes pour une seule personne : le concepteur du schéma. Ne jamais avoir peur de passer pour naïf. Au contraire, bien souvent une question anodine à priori entraîne une rectification du schéma. Preuve que l’exercice est utile.

Bien des points ne sont jamais documentés sur les schémas. Les temps de propagation, les impédances, les courants circulant dans les pistes ou encore la surface d’une "Exposed Pad" permettant d’évacuer des calories à travers les couches du PCB (encore un sujet intéressant), doivent être étudiés avant de passer à l’implantation.

Concevoir "Mécatronique"

Nous disposons de logiciels performants pour travailler, mais….

L’un des problèmes récurrant que j’ai souvent constaté, c’est l’impossibilité de faire "rentrer" l’électronique dans le boîtier mécanique conçu spécialement. Un comble aujourd’hui, alors que nous disposons d’un format d’échanges de fichiers universel permettant d’intégrer l’image 3D d’un circuit imprimé dans un dossier mécanique Autocad, Catia, SolidWorks et autre ProEngineer.

Donc, toujours exporter un projet d’implantation au format DXF aussitôt que possible et le faire valider. Cela ne prend que quelques minutes. Si votre interlocuteur ne valide pas une implantation, risquant ainsi de remettre en cause votre travail et le sien, il va y avoir un sérieux problème.

Le projet d’implantation ne contient que le contour du PCB, les connecteurs, les points de fixation et les composants ayant un encombrement critique. Ce n’est qu’un projet.

Une fois le projet de mécanique validé, le placement des composants peut commencer.

Utiliser le "crossprobing"

Sous ce terme un peu abscon se cache l’interactivité entre le schéma et le PCB.

Imaginez votre station de CAO équipée de deux écrans, l’un ouvert sur le schéma et l’autre ouvert sur le logiciel de placement. En pointant un composant sur le schéma, ce composant est sélectionné sur le PCB au milieu du chevelu et de l’amas de composants non placés. Et viceversa.

De la même manière, sélectionner une équipotentielle sur l’un des logiciels illumine celle-ci sur l’autre. Les éventuelles modifications sont prises en compte de l’un sur l’autre (plutôt pratique de faire des modifications pour améliorer le placement, non ?) en ayant la certitude de ne pas "oublier" l’une d’elles au passage…

Il est malheureux que cette fonction ne soit pas disponible systématiquement entre les logiciels d’édition de schémas et de PCB chez un même éditeur et qu’il soit souvent nécessaire d’acquérir un utilitaire additionnel (PCB Navigator de Precience par exemple) pour palier cette carence.

Cet éditeur revendique une réduction importante des défauts causés par des règles de conception non respectées et des erreurs lors des échanges de modifications (ECO). Je confirme.

Un bon conseil avant d’acheter un nouveau logiciel : vérifiez la présence de cette "option".

Conséquence : mettre en conformité les schémas du client avec les bibliothèques d’empreintes utilisées. Ceci n’est pas non plus sans incidence sur le résultat final.

Concevoir les empilages avant le routage

Pour beaucoup d’entre nous, concepteurs de circuits imprimés, la fabrication de ceux-ci se limitait à envoyer nos précieux fichiers Gerber avec un bon de commande à un fabricant de PCB. Conséquence, nous avons de plus en plus de circuits instables, ou qui ne fonctionnent pas. L’arrivé des normes RoHS et des nouveaux matériaux est probablement la cause de nos problèmes !

Pas si évident… Et à mon avis totalement faux.

La technologie a évolué ces dernières années. Concevoir des circuits dépassant allégrement le GigaHertz est devenu le quotidien de certains d’entre nous, et cela parfois sans maitriser le minimum de connaissances nécessaires à la conception de tels circuits. Rappelons qu’il n’y a pas de formation en la matière et que le métier d’implanteur est trop souvent considéré comme plus proche du dessin industriel que de l’intégrité du signal.

Un exemple ? Nous prenons trop souvent pour constante la vitesse de propagation des signaux électriques sur nos PCB comme égale à la moitié de la vitesse lumière. C’est un peu trop simple et, comme toujours dans nos métiers, source de pas mal de déboires…

Effectivement, si la vitesse de propagation dans un fil de cuivre est égale à la vitesse lumière, cette célérité est divisée par 9 si on trempe ce même conducteur dans l’eau. C’est stupide ? Oui, mais la démonstration est alors faite que la vitesse de propagation est directement fonction de la permittivité électrique du matériau environnant le conducteur, et non pas du conducteur luimême. Pour mémoire, la permittivité de l’eau douce à 25°C est de 78,5.

La vitesse de propagation des signaux dans un circuit "Stripline" est égale à : C/√εr

Avec C (vitesse lumière de 299.792.458 m/s suivant le bureau international des poids et mesures de Sèvres), donc la moitié de la vitesse lumière pour une permittivité électrique (εr) de 4 (Circuits HiTG, normes RoHS). Soit encore 150mm par nanoseconde ou 6,67 nanosecondes par mètre.

Avec un εr de 4,7 (Permittivité électrique habituelle des circuits FR4), la vitesse décroit à environ 138mm par nanoseconde. (Ici, refaire le calcul avec la permittivité de H2O…)

On voit ici l’incidence directe de la permittivité électrique du milieu, ce qui peut expliquer quelques problèmes sur des circuits imprimés où les tolérances sur les lignes différentielles sont de 125μm ou 5 mils (Cartes PCI Express de nos ordinateurs par exemple).

Encore que j’ai simplifié le problème, car je n’ai considéré que le cas d’une Stripline (Couche interne) avec une épaisseur de diélectrique identique sur les deux faces. Pour les couches externes, le problème est plus complexe du fait de l’environnement hétérogène (Air et FR4) entourant le conducteur. La célérité est alors comprise entre la vitesse de la lumière et cette même vitesse divisée par la racine carrée de la permittivité de l’isolant. En gros, une multiplication par 0,94 donne des résultats moyens, soit une célérité de 145mm par nanoseconde pour une piste de 100μ et un εr de 4.

Nous avons démontré ici l’importance du choix des matériaux, venons en au respect des impédances qui trop souvent est laissé à la charge du fabricant de PCB.

Face à notre problème d’impédances, le fabricant de PCB nous proposera des circuits réalisés avec une "impédance contrôlée". Terme magique ! Solution toute faite ! Mais de quoi s’agit-il exactement ? Le fabricant de PCB va demander quelles sont les impédances à respecter, puis va régler ses diélectriques et ses empilages au mieux pour respecter les exigences. Et si ce n’est pas suffisant, il va "recharger" ou "amincir" les pistes pour obtenir le résultat souhaité. Sympa non ? Mais ceci n’est, bien sûr, valable que pour une impédance caractéristique, sur une surface réduite. Si on doit contrôler des lignes différentielles (USB, PCIe, SATA, HDMI, Ethernet), des lignes asymétriques rapides (Mémoires SDRAM ou DDR), des coaxiaux (Reprises d’antennes pour modules GSM, GPS, WiFi, ZigBee) il faut remettre en cause ses habitudes de travail et gérer soimême ses impédances, et ensuite exiger le respect de celles-ci.

J’utilise personnellement en ligne une feuille de calcul permettant de réaliser rapidement les calculs d’impédance. Sans vouloir rivaliser avec les outils professionnels tels que ceux de Polar Instruments, les formules utilisées donnent des résultats approximatifs (mais assez justes) qui devront être affinés si une plus grande précision était requise. Voir tableau en exemple ci-contre.

Quelques bonus intégrés à ce tableau qui m’aident bien en cours de travail :

![]() Le courant admissible pour une élévation de température

donnée dans une piste.

Le courant admissible pour une élévation de température

donnée dans une piste.

![]() La résistance de la piste est calculée en fonction de tous

les paramètres entrés.

La résistance de la piste est calculée en fonction de tous

les paramètres entrés.

![]() Le courant admissible pour une élévation de température

donnée dans un via.

Le courant admissible pour une élévation de température

donnée dans un via.

C’est toujours par la conception de l’empilage qu’il faut commencer, car l’impédance des pistes routées, et donc leur épaisseur, leur isolation dépendent largement de ce travail.

C’est une révolution culturelle pour de nombreux implanteurs qui commençaient leur travail par l’implantation des composants et finissaient généralement par les plans d’alimentation et les calculs d’impédance.

Le circuit imprimé double face est à proscrire définitivement pour les réalisations complexes, sauf si l’investissement pour la conception sur de tels circuits est justifié par le volume de production. Il faut savoir que la conception de tels circuits est complexe si l’on veut respecter les exigences de la directive "Basse Tension" en matière de rayonnement et d’immunité (marquage CE) et que la mise au point risque d’être assez longue.

Le quatre couches est un empilage symétrique parfait pour les circuits imprimés supportant une densité de composants raisonnable. Mais, si on réserve une couche interne pour le plan de masse, et l’autre pour les alimentations, il ne reste que les deux faces externes pour supporter les composants et les pistes routées. Il est possible d’augmenter la densité du routage en passant les plans d’alimentation et de masse sur les couches externes, mais ceci impose de n’avoir aucune rupture du plan de masse (pas de composants en face "soudure") et des plans d’alimentation qui recouvriront la face composants. Peu d’électroniciens apprécient cette configuration en raison des difficultés de mise au point. Pourtant, cet inconvénient est largement compensé par les excellents résultats obtenus en rayonnement et en immunité.

Le six couches doit être utilisé avec beaucoup de précautions en raison de problèmes d’intégrité du signal. Les signaux étant toujours référencés à un plan (GND ou VCC par exemple), il vaut mieux ne pas en être trop éloigné. Contrôler les impédances devient plus difficile. Ici encore, une feuille de calcul paramétrée pour une construction asymétrique sera utilisée avec profit. Par construction, le rapport nombre de couches / prix de revient n’est pas très concurrentiel.

Il est beaucoup plus économique de revenir au quatre couches et passer en technologie HDI (Microvias). Ceci fera l’objet d’un prochain article.

Le huit couches est un compromis parfait assurant une excellente symétrie et permettant une très forte densité d’implantation et de routage. Il n’est pas beaucoup plus cher qu’un six couches.

Les autres configurations seront utiles si l’intégration devient vraiment très forte. L’utilisation de circuits BGA à pas de 0,8mm (au-delà, il faudra passer aux vias laser conjugués avec des vias enterrés) peut nécessiter de passer à des circuits de 12 couches et parfois plus. Dans ce cas, l’impact économique doit être examiné avec le client à ce stade et surtout pas plus tard.

Intégrer les contraintes de routage et les contraintes thermiques

Les contraintes ont été fixées et acceptées lors de la revue de schémas. Il faut les rentrer dans le logiciel de placement de telle façon qu’elles soient respectées durant le routage sous peine de générer des erreurs.

Les contraintes sont multiples. Pour ne citer que les plus courantes :

![]() Impédance des pistes de type microstrip ou stripline

Impédance des pistes de type microstrip ou stripline

![]() Impédance des lignes différentielles haute vitesse

Impédance des lignes différentielles haute vitesse

![]() Temps de propagation des bus synchrones et des horloges

Temps de propagation des bus synchrones et des horloges

![]() Isolation minimum (raisonnable et justifiée) des équipotentielles

entre elles

Isolation minimum (raisonnable et justifiée) des équipotentielles

entre elles

![]() Courant maximum admissible dans les pistes pour une

élévation de température donnée (Comment, un cuivre

ça chauffe ?)

Courant maximum admissible dans les pistes pour une

élévation de température donnée (Comment, un cuivre

ça chauffe ?)

![]() Dissipation thermique à assurer par les semelles des

composants de puissance

Comme vous le remarquerez, j’ai abandonné depuis

longtemps la notion de "classe de routage" telle que définie

dans la norme NFC 93-713 obsolète mais hélas

encore officielle.

Dissipation thermique à assurer par les semelles des

composants de puissance

Comme vous le remarquerez, j’ai abandonné depuis

longtemps la notion de "classe de routage" telle que définie

dans la norme NFC 93-713 obsolète mais hélas

encore officielle.

Depuis longtemps, j’ai décidé de refuser de travailler avec des fabricants de PCB qui se réfèrent à celle-ci. Heureusement lorsqu’ils sont performants, ils ont depuis longtemps oublié une norme datant du siècle dernier qui ne citait la classe 6 qu’à titre prospectif !

Systématiser l’emploi des empreintes tel que recommandé par l’IPC

Ici, je rends hommage à l’excellent travail réalisé par PCB Matrix sur la génération d’empreintes conformes aux recommandations de l’association IPC et la mise à disposition gratuite de son logiciel LP Calculator. La standardisation des empreintes (Land Pattern) avait toujours achoppé en raison de l’hostilité des éditeurs de logiciels de CAO (25% des licences seraient utilisées pour la gestion des bibliothèques de composants, ceci expliquant peut-être cela). La version payante de cet utilitaire permet de palier cet inconvénient en générant automatiquement des bibliothèques normalisées au format de votre logiciel préféré.

Les générateurs d’empreintes automatiques intégrés dans certains logiciels ne permettent pas de prendre en compte la densité des composants et de réduire (ou d’augmenter) celle-ci selon le process d’assemblage de la carte électronique. L’utilisation de bibliothèques nominales, haute et faible densité pour les composants en montage de surface permet d’adapter en fonction des besoins et des possibilités de la chaîne d’assemblage la densité d’intégration sur le PCB.

Le système de "nomage" des empreintes préconisé par PCB Matrix a le mérite de standardiser également le nom des composants. Personnellement, je préfère les appellations Jedec. A chacun ses choix, mais une méthode unique dans l’entreprise (et reprise dans le système qualité ! Un must) n’est pas un luxe.

Recevoir un schéma impeccable mais devoir reprendre les caractéristiques de tous les composants pour leur donner un nom compatible avec les bibliothèques existantes, c’est vraiment frustrant.

Il est vrai également que beaucoup d’industriels ont passé beaucoup de temps sur la validation de leurs process de production et qu’ils exigent l’emploi de leur bibliothèque d’empreintes si laborieusement mise au point. J’oserai dire que c’est dommage de ne pas profiter de l’expérience de l’association IPC, qui rassemble dans ses recommandations (non, ce ne sont pas des normes, justes des recommandations) l’expérience de milliers d’adhérents.

Passer au routage sous contraintes

Travailler sous contraintes n’est pas si facile mais c’est la seule solution pour respecter les exigences du concepteur. Lorsqu’il y a trop d’équipotentielles, on perd très vite le fil de ses idées et seul le logiciel peut nous rappeler une violation de contrainte.

Peu d’éditeurs de logiciels ont intégré le routage sous contraintes dans les versions de base de leurs produits. C’est souvent une option "haut de gamme" malheureusement. Par contre, ils intègrent souvent des règles de vérification de ces contraintes.

C’est bien-sûr fastidieux (et non prévu dans le budget, comme d’habitude) de rentrer les contraintes de routage des signaux pour pouvoir ensuite vérifier et valider le travail réalisé. Mais comment faire autrement ? De toute façon, il va falloir vérifier, vérifier, et vérifier encore…. Ici, les automatismes du logiciel seront d’une grande aide, surtout s’il est prévu d’exécuter une passe de vérification d’intégrité du signal après routage.

L’intégrité du signal

Sous ce terme barbare se cache la validation des circuits électroniques composés de l’étage de sortie d’un composant, du circuit imprimé et de l’étage d’entrée du ou des composants recevant le signal.

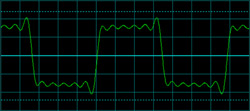

Imaginons un signal carré à 100Mhz. Un signal carré est un signal complexe de fréquence fondamentale F (ici 100Mhz) sur lequel se superposent des harmoniques de rang N. Sur ce premier chronogramme, j’ai limité le signal à l’harmonique 11. Le signal est assez propre pour servir d’horloge à de nombreux circuits digitaux.

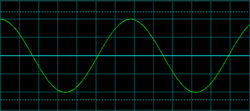

Prenons le même signal carré à 100Mhz et admettons que le routage de sa piste ne permette pas de passer 300Mhz (piste très capacitive). Le chronogramme cicontre nous montre une jolie fondamentale sans harmoniques. On est assez loin du résultat attendu.

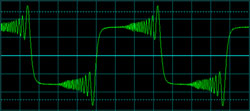

Continuons. A droite, nous avons toujours notre fondamentale de 100Mhz avec toutes les harmoniques jusqu’à 3Ghz, avec le même léger déphasage en haute fréquence que sur la première figure, à cause de capacité parasites, et là, nous nous trouvons en face de rebonds qui vont très sérieusement perturber le fonctionnement de circuits synchrones.

S’il y a un domaine à creuser pour le bon fonctionnement des circuits électroniques, c’est bien celui de l’intégrité du signal, comme le montre cet exemple.

Conclusion

Il n’était pas question de faire ici un cours magistral sur la conception de PCB, ni sur l’intégrité du signal. Juste rappeler qu’il existe des lois physiques avec lesquelles il nous faut composer si nous souhaitons améliorer le comportement des produits que nous concevons. De bonnes pratiques doivent en découler. Certaines sont acquises, d’autres devront l’être. La spécialité d’ingénieur en conception de circuits imprimés, oui j’ai bien écrit ingénieur, doit être reconnue comme telle, et valorisée comme telle, au même titre que celle d’ingénieur électronicien. Les technologies sur lesquelles nous travaillons sont très complexes et les outils que nous employons justifient amplement cette qualification.

Coter un travail à XX Euros l’équivalent 14 broches sans connaître le fonctionnement d’un circuit et l’impact de la conception du PCB sur le fonctionnement du montage est une hérésie. De même que s’accrocher à la norme NFC 93-713 est aujourd’hui totalement obsolète.

Je me souviens qu’en 1986, j’ai commencé à utiliser l’un des tous premiers logiciels de Conception Assistée de PCB sur PC (SmartWork). La sortie se faisait sur table traçante, avec des stylos Rotring et des encres denses chargées au latex. J’ai montré mes "typons" à un bureau d’études qui travaillait encore avec des pistes et des pastilles, et je leur ai demandé s’il était possible de fabriquer un PCB à partir de ces documents. J’ai été brocardé comme rarement dans ma vie. J’ai alors rencontré Alain Milard (le monde est petit !) qui a photographié mes typons et a généré les films dont j’avais besoin. Lui ne riait pas. Un an plus tard, ma CAO générait des Gerbers phototracés par Delta Chrome.

Notre profession évolue. Il est nécessaire que nous continuions à évoluer avec elle.

Email de Jean Pierre JOSSE :